## EE 330 Lecture 41

### **Digital Circuits**

Overdrive Factors

Propagation Delay With Multiple Levels of Logic

### **Exam Schedule**

Exam 1 Friday Sept 24

Exam 2 Friday Oct 22

Exam 3 Friday Nov 19

Final Tues Dec 14 12:00 p.m.

As a courtesy to fellow classmates, TAs, and the instructor

Wearing of masks during lectures and in the laboratories for this course would be appreciated irrespective of vaccination status

### Final Tues Dec 14 (scheduled 12:00 pm)

Final Exam will be distributed by 8:00 AM on the day of exam and due on Canvas at 2:15 PM

This will be structured as a 2-hour in-person exam following the same format as the final exam from previous semesters that are posted on the class website.

Students will be expected to comply with the honor system as stipulated on previous exams in this course. If anyone is unwilling to comply with the honor system, please let me know by Friday December 10 so that alternative arrangements can be made for taking the final exam. A grade of 0 along with other sanctions will be assessed for anyone that does not comply with the honor system on this exam.

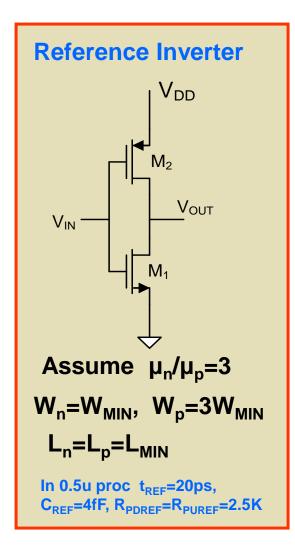

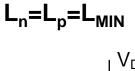

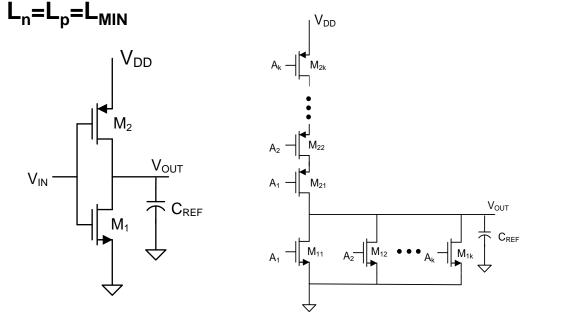

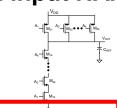

### The Reference Inverter

$$R_{PDREF} = R_{PUREF}$$

$C_{REF} = C_{IN} = 4C_{OX}W_{MIN}L_{MIN}$

$$R_{\text{PDREF}} = \frac{L_{\text{MIN}}}{\mu_{\text{n}} C_{\text{OX}} W_{\text{MIN}} \left(V_{\text{DD}} \text{-} V_{\text{Tn}}\right)} \stackrel{V_{\textit{Tn}} = .2 V_{\textit{DD}}}{=} \frac{L_{\text{MIN}}}{\mu_{\text{n}} C_{\text{OX}} W_{\text{MIN}} \left(0.8 V_{\text{DD}}\right)}$$

$$t_{HLREF} = t_{LHREF} = R_{PDREF}C_{REF}$$

$$t_{REF} = t_{HLREF} + t_{LHREF} = 2R_{PDREF}C_{REF}$$

(Note: This  $C_{OX}$  is somewhat larger than that in the 0.5u ON process)

# Device Sizing

**Equal Worse-Case Rise/Fall Device Sizing Strategy**

-- (same as V<sub>TRIP</sub>=V<sub>DD</sub>/2 for worst case delay in typical process considered in example)

Assume  $\mu_n/\mu_p=3$  How many degrees of freedom were available?

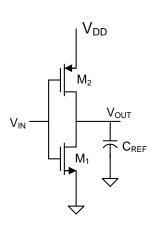

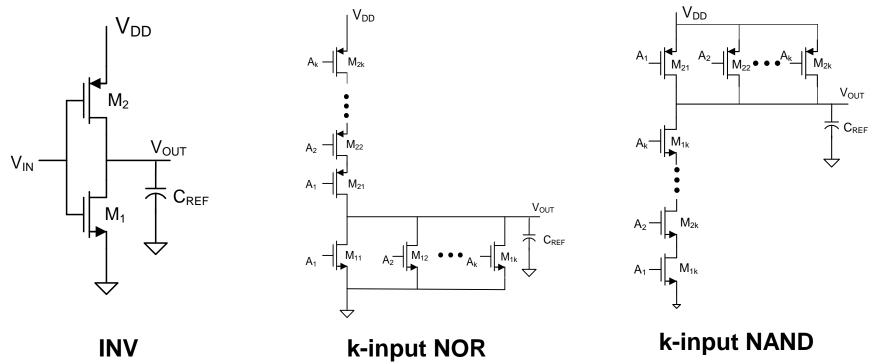

#### INV

$$W_n = W_{MIN}, W_p = 3W_{MIN}$$

FI=1

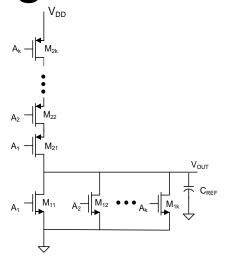

#### k-input NOR

$$W_n = W_{MIN}, W_p = 3kW_{MIN}$$

$$\mathbf{C}_{\mathsf{IN}} = \left(\frac{3\mathsf{k}+1}{4}\right) \mathbf{C}_{\mathsf{REF}}$$

$$\mathsf{FI} = \left(\frac{3\mathsf{k}+1}{4}\right)$$

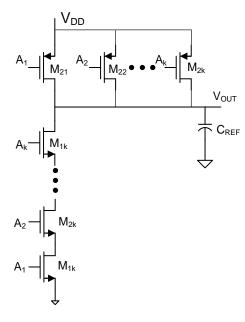

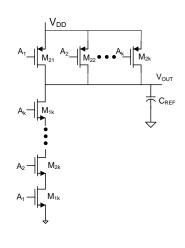

#### k-input NAND

$$W_n = kW_{MIN}, W_p = 3W_{MIN}$$

$$\mathbf{C}_{\mathsf{IN}} = \left(\frac{3+\mathsf{k}}{4}\right) \mathbf{C}_{\mathsf{REF}}$$

$$FI = \left(\frac{3+k}{4}\right)$$

# Device Sizing

#### **Multiple Input Gates:**

2-input NOR

k-input NOR

k-input NAND

Equal Worst Case Rise/Fall (and equal to that of ref inverter when driving C<sub>REF</sub>)

Wn=?

Wp=?

Fastest response  $(t_{HL} \text{ or } t_{LH}) = ?$

Worst case response ( $t_{PROP}$ , usually of most interest)?

Input capacitance (FI) = ?

Minimum Sized (assume driving a load of C<sub>REF</sub>)

Wn=Wmin

Wp=Wmin

Fastest response  $(t_{HL} \text{ or } t_{LH}) = ?$

Slowest response  $(t_{HL} \text{ or } t_{LH}) = ?$

Worst case response ( $t_{PROP}$ , usually of most interest)?

Input capacitance (FI) = ?

### Device Sizing - minimum size driving CREF

#### INV

# $t_{PROP} = 0.5t_{REF} + \frac{3}{2}t_{REF}$ $t_{PROP} = 2t_{REF}$

#### k-input NOR

$$t_{PROP} = 0.5t_{REF} + \frac{3k}{2}t_{REF}$$

$$t_{PROP} = \left(\frac{3k+1}{2}\right)t_{REF}$$

#### k-input NAND

$$t_{PROP} = \frac{3}{2}t_{REF} + \frac{k}{2}t_{REF}$$

$$t_{PROP} = \frac{3+k}{2}t_{REF}$$

$$FI = \frac{C_{REF}}{2}$$

$$R_{PU} = 3R_{PDREF}$$

$$R_{PD} = R_{PDREF}$$

$$\frac{1+3k^{2}}{2k}t_{REF} \leq t_{PROP} \leq \frac{3k+1}{2}t_{REF}$$

$$FI = \frac{C_{REF}}{2}$$

$$\frac{R_{PDREF}}{k} \leq R_{PD} \leq R_{PDREF}$$

$$R_{PU} = 3kR_{PDREF}$$

$$\frac{3+k^{2}}{2k}t_{REF} \leq t_{PROP} \leq \frac{3+k}{2}t_{REF}$$

$$FI = \frac{C_{REF}}{2}$$

$$\frac{3R_{PDREF}}{k} \leq R_{PU} \leq 3R_{PDREF}$$

$$R_{PD} = kR_{PDREF}$$

# Device Sizing Summary

$C_{\text{IN}}$  for  $N_{\text{AND}}$  gates is considerably smaller than for NOR gates for equal worst-case rise and fall times

$C_{IN}$  for minimulm-sized structures is independent of number of inputs and much smaller than  $C_{IN}$  for the equal rise/fall time case

R<sub>PII</sub> gets very large for minimum-sized NOR gate

#### **Review from Last Time**

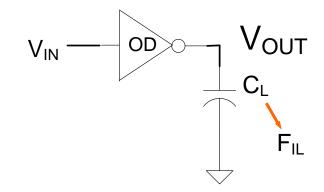

### Propagation Delay with Stage Loading

$$t_{REF} = 2R_{PDref}C_{REF}$$

$$C_{REF} = 4C_{OX}W_{MIN}L_{MIN}$$

FI of a capacitor

FI of an interconnect

$$FI_C = \frac{C}{C_{REF}}$$

$$\mathsf{FI}_{\mathsf{G}} = \frac{\mathsf{C}_{\mathsf{INk}}}{\mathsf{C}_{\mathsf{REF}}}$$

$$FI_{l} = \frac{C_{INI}}{C_{RFF}}$$

$$\text{FI} = \frac{\displaystyle\sum_{\text{Gates}} C_{\text{INGi}} + \displaystyle\sum_{\text{Capacitances}} C_{\text{INCi}} + \displaystyle\sum_{\text{Interconnects}} C_{\text{INIi}}}{C_{\text{REF}}}$$

FI can be expressed either in units of capacitance or normalized to  $C_{\mathsf{REF}}$

Most commonly FI is normalized but must determine from context

If gates sized to have same drive as ref inverter

$$t_{prop-k} = t_{REF} \bullet FI_{LOAD-k}$$

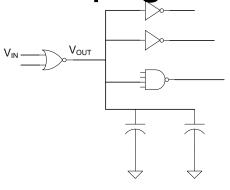

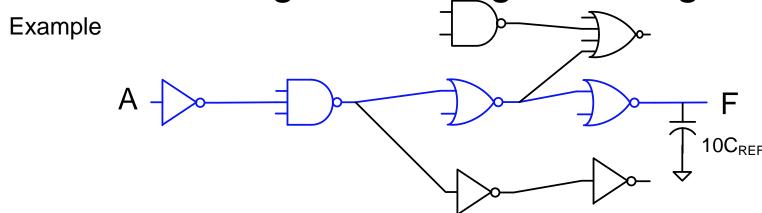

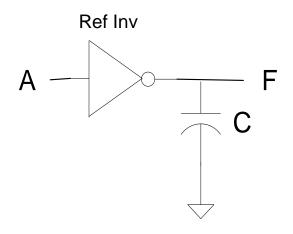

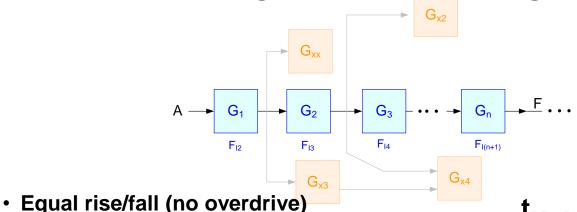

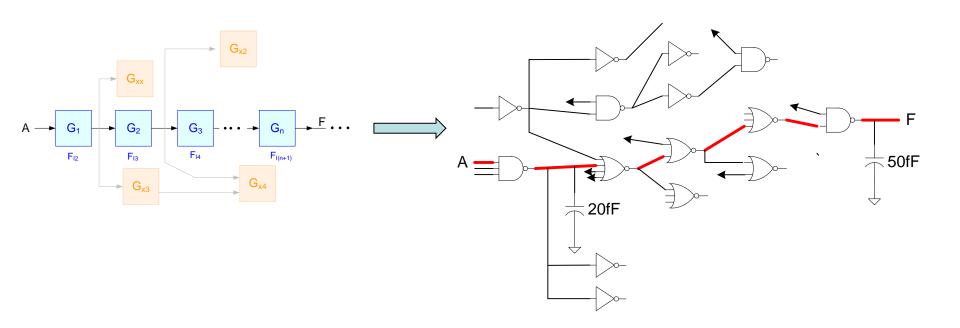

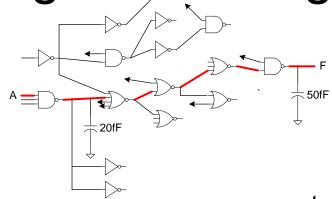

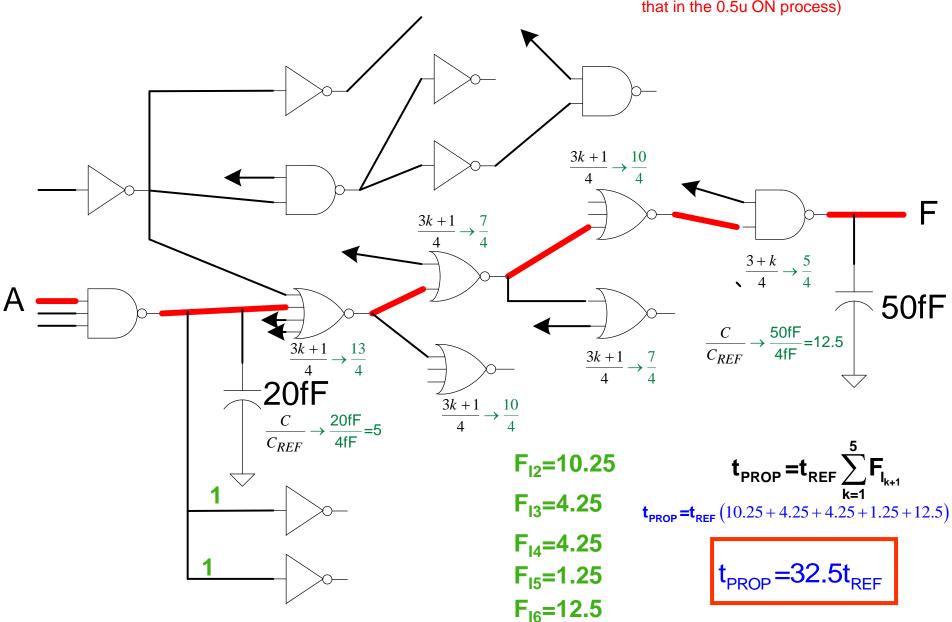

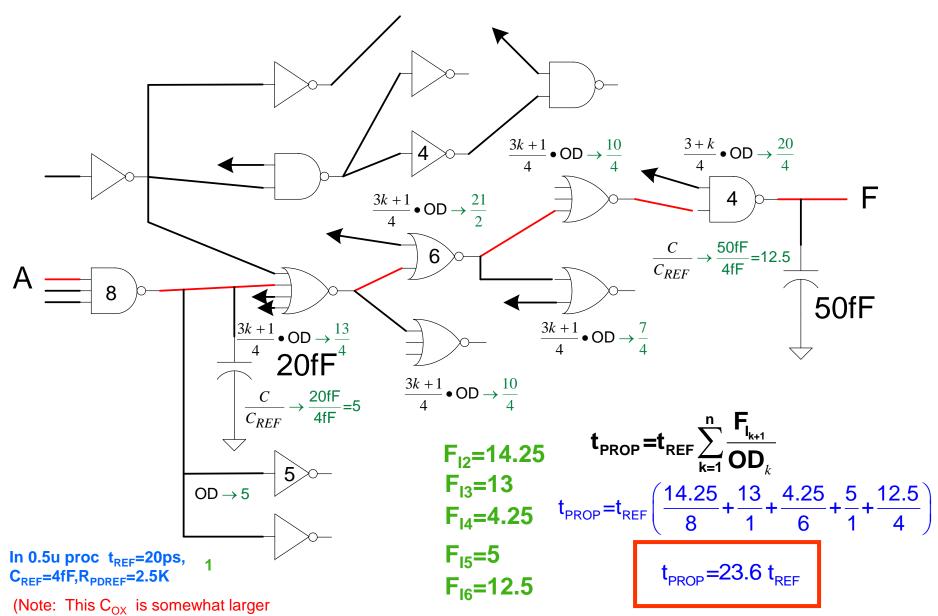

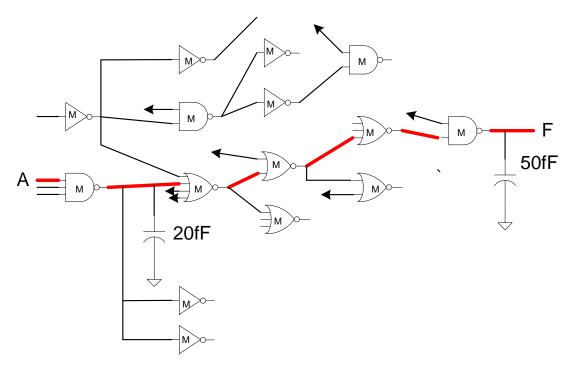

Assume all gates sized for equal worst-case rise/fall times Assume all gate drives are the same as that of reference inverter Neglect interconnect capacitance, assume load of 10C<sub>RFF</sub> on F output

Determine propagation delay from A to F

$$\begin{aligned} \mathsf{FI}_2 = & \frac{6}{4} \, \mathsf{C}_{\mathsf{REF}} & \mathsf{FI}_3 = & \mathsf{C}_{\mathsf{REF}} + \frac{7}{4} \, \mathsf{C}_{\mathsf{REF}} & \mathsf{FI}_4 = & \frac{7}{4} \, \mathsf{C}_{\mathsf{REF}} + \frac{13}{4} \, \mathsf{C}_{\mathsf{REF}} & \mathsf{FI}_5 = & \mathsf{10C}_{\mathsf{REF}} \\ t_{\mathsf{PROP1}} = & \frac{6}{4} \, t_{\mathsf{REF}} & t_{\mathsf{PROP2}} = & \left(1 + \frac{7}{4}\right) t_{\mathsf{REF}} & t_{\mathsf{PROP3}} = & \left(\frac{7}{4} + \frac{13}{4}\right) t_{\mathsf{REF}} & t_{\mathsf{PROP4}} = & \mathsf{10t}_{\mathsf{REF}} \\ t_{\mathsf{PROP4}} = & \sum_{\mathsf{Ind}} t_{\mathsf{PROPk}} = t_{\mathsf{REF}} \sum_{\mathsf{Ind}} \mathsf{FI}_{(\mathsf{Ik+1})} = t_{\mathsf{REF}} \left(\frac{6}{4} + \frac{11}{4} + \frac{20}{4} + \mathsf{10}\right) = t_{\mathsf{REF}} \left(\mathsf{19.25}\right) \end{aligned}$$

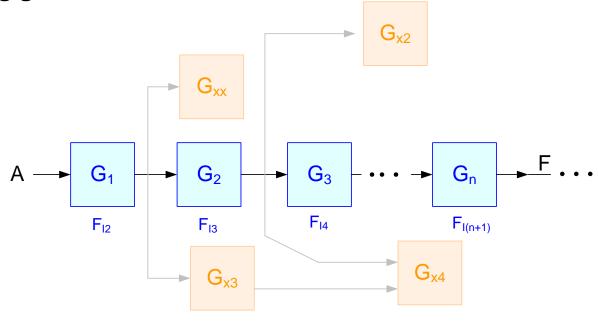

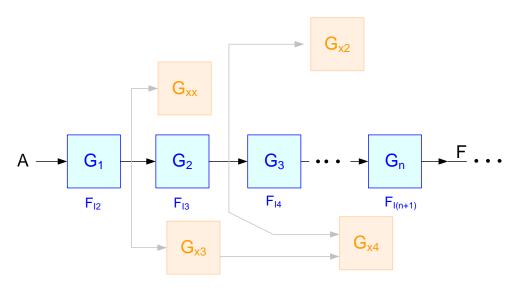

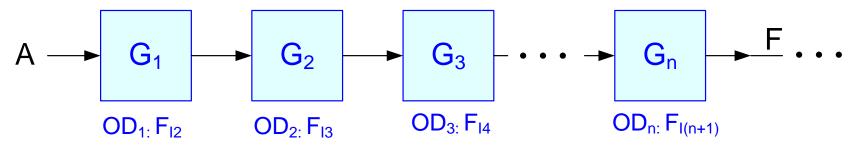

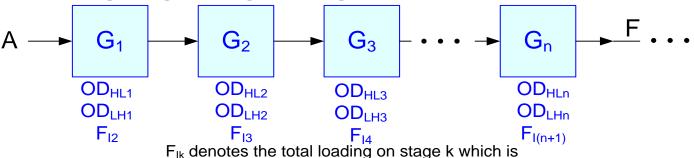

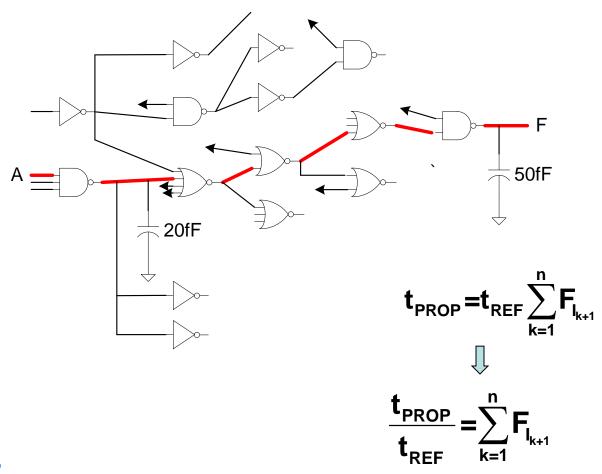

# Propagation Delay Through Multiple Stages of Logic with Stage Loading

(assuming gate drives are all same as that of reference inverter)

Identify the gate path from A to F

$$t_{PROPk} = t_{REF} FI_{(k+1)}$$

Propagation delay from A to F:

$$t_{PROP} = t_{REF} \sum_{k=1}^{n} FI_{(k+1)}$$

This approach is analytically manageable, provides modest accuracy and is "faithful"

## Digital Circuit Design

- Hierarchical Design

- Basic Logic Gates

- Properties of Logic Families

- Characterization of CMOS Inverter

- Static CMOS Logic Gates

- Ratio Logic

- Propagation Delay

- Simple analytical models

- FI/OD

- Logical Effort

- Elmore Delay

- Sizing of Gates

- The Reference Inverter

- Propagation Delay with Multiple Levels of Logic

- Optimal driving of Large Capacitive Loads

- Power Dissipation in Logic Circuits

- Other Logic Styles

- Array Logic

- Ring Oscillators

done

partial

# What if the propagation delay is too long (or too short)?

#### Propagation delay from A to F:

$$t_{PROP} = t_{REF} \sum_{k=1}^{n} FI_{(k+1)}$$

$$t_{PROPk} = t_{REF} FI_{(k+1)}$$

#### Recall:

# Device Sizing

**Multiple Input Gates:**

2-input NOR

Equal Worst Case Rise/Fall (and equal to that of ref inverter when driving C<sub>REF</sub>)

$$W_n=?$$

$$W_p = ?$$

Fastest response  $(t_{HI} \text{ or } t_{IH}) = ?$

Worst case response ( $t_{PROP}$ , usually of most interest)?

Input capacitance (FI) = ?

Minimum Sized (assume driving a load of CREF)

$$W_n = W_{min}$$

$$W_p = W_{min}$$

Fastest response  $(t_{HI} \text{ or } t_{IH}) = ?$

Slowest response  $(t_{HL} \text{ or } t_{LH}) = ?$

Worst case response ( $t_{PROP}$ , usually of most interest)?

Input capacitance (FI) = ?

#### Recall:

## Device Sizing

Equal Worst Case Rise/Fall | (and equal to that of ref inverter when driving C<sub>REF</sub>)

$V_{DD}$

(n-channel devices sized same, p-channel devices sized the same) Assume L<sub>n</sub>=L<sub>p</sub>=Lmin and driving a load of C<sub>REF</sub>

$$W_n=?$$

$W_p = ?$

Input capacitance = ?

**FI=?**

t<sub>PROP</sub>=? (worst case)

#### $W_n = W_{MIN}$

$W_n = 6W_{MIN}$

#### **DERIVATIONS**

One degree of freedom was used to

satisfy the constraint indicated

Other degree of freedom was used to achieve equal rise and fall times

$$C_{INA} = C_{INB} = C_{OX} W_{MIN} L_{MIN} + 6C_{OX} W_{MIN} L_{MIN} = 7C_{OX} W_{MIN} L_{MIN} = \left(\frac{7}{4}\right) 4C_{OX} W_{MIN} L_{MIN} = \left(\frac{7}{4}\right) C_{REF}$$

$$FI = \left(\frac{7}{4}\right) C_{REF}$$

or  $FI = \frac{7}{4}$

$$t_{PROP} = t_{REF}$$

(worst case)

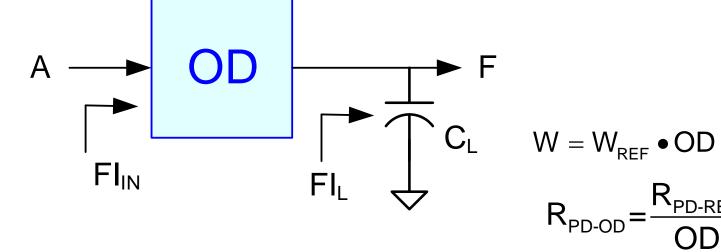

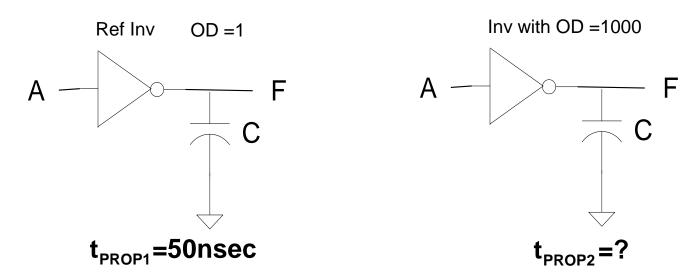

### Overdrive Factors

Example: Determine  $t_{prop}$  in 0.5u process if C=10pF In 0.5u proc  $t_{REF}$ =20ps,  $C_{REF}$ =4fF, $R_{PDREF}$ =2.5K

$$\mathbf{t}_{\mathsf{PROP}} = \mathbf{t}_{\mathsf{REF}} \bullet \mathsf{FI} = \mathbf{t}_{\mathsf{REF}} \bullet \frac{10pF}{4fF} = \mathbf{t}_{\mathsf{REF}} \bullet 2500$$

$$t_{PROP} = 20ps \cdot 2500 = 50nsec$$

Note this is unacceptably long!

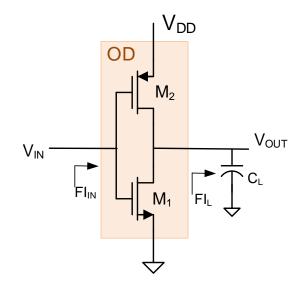

### Overdrive Factors

Scaling widths of ALL devices by constant (W<sub>scaled</sub>=WxOD) will change "drive" capability relative to that of the reference inverter but not change relative value of  $t_{HL}$  and  $t_{LH}$

$$R_{PD} = \frac{L_{1}}{\mu_{n} C_{OX} W_{1} (V_{DD} - V_{Tn})} = \frac{R_{PD}}{OD}$$

$$R_{PDOD} = \frac{L_{1}}{\mu_{n} C_{OX} [OD \bullet W_{1}] (V_{DD} - V_{Tn})} = \frac{R_{PD}}{OD}$$

$$R_{PDOD} = \frac{L_1}{\mu_n C_{OX} [OD \bullet W_1] (V_{DD} - V_{Tn})} = \frac{R_{PD}}{OD}$$

$$R_{PUOD} = \frac{L_2}{\mu_p C_{OX} W_2 \left( V_{DD} + V_{Tp} \right)} = \frac{R_{PU}}{OD}$$

$$R_{PUOD} = \frac{L_2}{\mu_p C_{OX} [OD \bullet W_2] (V_{DD} + V_{Tp})} = \frac{R_{PU}}{OD}$$

$$t_{PROP} = t_{REF} \cdot FI_{L} \cdot \frac{1}{OD}$$

Scaling widths of ALL devices by constant will change Fl<sub>IN</sub> to gate by OD

$$C_{IN} = C_{OX} (W_1 L_1 + W_2 L_2)$$

$$C_{\text{INOD}} = C_{\text{OX}} ([O D \bullet W_1] L_1 + [O D \bullet W_2] L_2) = O D \bullet C_{\text{IN}}$$

### Overdrive Factors - Summary

(For equal worst-case rise/fall gates)

$$t_{PROP} = t_{REF} \cdot FI_{L} \cdot \frac{1}{OD}$$

$$FI_{IN} = OD \cdot C_{REF}$$

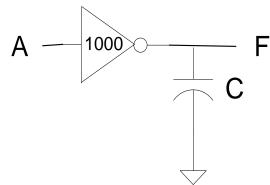

### **Overdrive Factors**

Example: Determine  $t_{prop}$  in 0.5u process if C=10pF and OD=1000

$$\mathbf{t_{PROP1}} = \mathbf{t_{REF}} \bullet \mathbf{FI} \bullet \frac{1}{\mathbf{OD}} = \mathbf{t_{REF}} \bullet \frac{10pF}{4fF} = \mathbf{t_{REF}} \bullet 2500$$

$$\mathbf{t_{PROP2}} = \mathbf{t_{REF}} \bullet \mathbf{FI} \bullet \frac{1}{\mathbf{OD}} = \mathbf{t_{REF}} \bullet \frac{10pF}{4fF} \bullet \frac{1}{\mathbf{1000}} = \mathbf{t_{REF}} \bullet 2.5$$

Note sizing the inverter with the OD improved delay by a factor of 1000!

### **Overdrive Factors**

- By definition, the factor by which the W/L of all devices are scaled above those of the reference inverter is termed the overdrive factor, OD

- Scaling widths by overdrive factor DECREASES resistance by same factor

- Scaling all widths by a constant does not compromise the symmetry between the rise and fall times (i.e.  $t_{HL}=t_{LH}$ )

- Judicious use of overdrive can dramatically improve the speed of digital circuits

- Large overdrive factors are often used

- Scaling widths by overdrive factor INCREASES input capacitance by same factor - So is there any net gain in speed?

## Digital Circuit Design

Hierarchical Design

Basic Logic Gates

Properties of Logic Families

Characterization of CMOS Inverter

Static CMOS Logic Gates

Ratio Logic

Propagation Delay

Simple analytical models

- FI/OD

- Logical Effort

- Elmore Delay

Sizing of Gates

The Reference Inverter

Propagation Delay with Multiple Levels of Logic

Optimal driving of Large Capacitive Loads

Power Dissipation in Logic Circuits

- Other Logic Styles

- Array Logic

- Ring Oscillators

done

partial

### Propagation Delay with Over-drive Capability

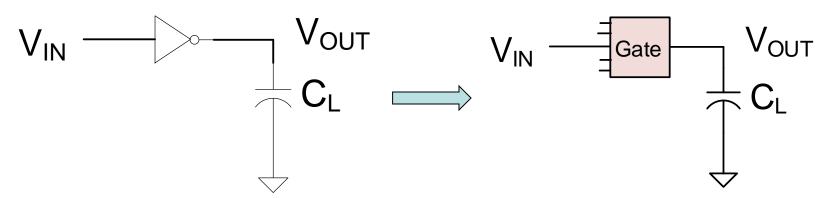

#### **Asymmetric Overdrive**

Define the Asymmetric Overdrive Factors of the stage to be the factor by which PU and PD resistors are scaled relative to those of the reference inverter.

$$R_{PDEFF} = \frac{R_{PDREF}}{OD_{HL}}$$

$$R_{PUEFF} = \frac{R_{PUREF}}{OD_{LH}}$$

$$t_{HL} = \frac{R_{PDREF}}{OD_{LH}}C_{L}$$

$$t_{LH} = \frac{R_{PDREF}}{OD_{LH}}C_{L}$$

$$\boldsymbol{t_{\mathsf{PROP}}} = \boldsymbol{t_{\mathsf{HL}}} + \boldsymbol{t_{\mathsf{LH}}} = \frac{\boldsymbol{R_{\mathsf{PDREF}}}}{\boldsymbol{\mathsf{OD}}_{\mathit{HL}}} \boldsymbol{C_{\mathsf{L}}} + \frac{\boldsymbol{R_{\mathsf{PDREF}}}}{\boldsymbol{\mathsf{OD}}_{\mathit{LH}}} \boldsymbol{C_{\mathsf{L}}} = \boldsymbol{R_{\mathsf{PDREF}}} \boldsymbol{C_{\mathsf{L}}} \left[ \frac{1}{\boldsymbol{\mathsf{OD}}_{\mathit{HL}}} + \frac{1}{\boldsymbol{\mathsf{OD}}_{\mathit{LH}}} \right] = \frac{\boldsymbol{t_{\mathsf{REF}}}}{2} \left[ \frac{1}{\boldsymbol{\mathsf{OD}}_{\mathit{HL}}} + \frac{1}{\boldsymbol{\mathsf{OD}}_{\mathit{LH}}} \right] \boldsymbol{F_{\mathsf{IL}}}$$

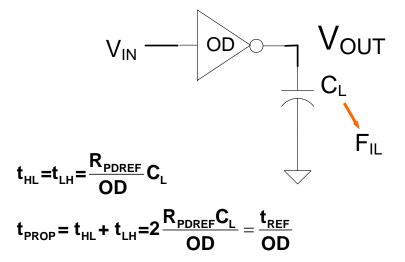

### Propagation Delay with Over-drive Capability

**Overdrive**

If an inverter with OD is sized for equal rise/fall,  $OD_{HL}=OD_{LH}=OD$

$$\mathbf{t}_{\mathsf{PROP}} = \mathbf{R}_{\mathsf{PDREF}} \mathbf{C}_{\mathsf{L}} \left[ \frac{1}{\mathsf{OD}_{HL}} + \frac{1}{\mathsf{OD}_{LH}} \right] = \mathbf{R}_{\mathsf{PDREF}} \mathbf{C}_{\mathsf{L}} \frac{\mathbf{2}}{\mathsf{OD}} = \mathbf{t}_{\mathsf{REF}} \frac{\mathbf{F}_{\mathsf{IL}}}{\mathsf{OD}}$$

OD may be larger or smaller than 1

### Propagation Delay with Over-drive Capability

#### **Example**

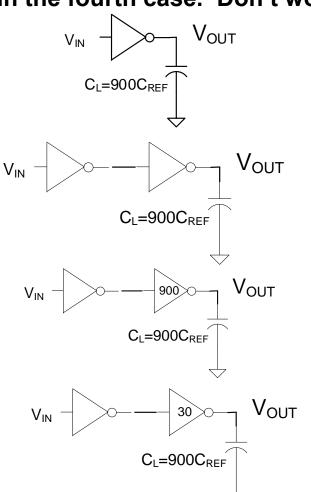

Compare the propagation delays. Assume the OD is 900 in the third case and 30 in the fourth case. Don't worry about the extra inversion at this time.

$$t_{\text{PROP}} \text{=}\ t_{\text{REF}} + 900t_{\text{REF}} = 901t_{\text{REF}}$$

$$t_{\text{PROP}} \hspace{-2pt}=\hspace{-2pt} 900t_{\text{REF}} + t_{\text{REF}} = \hspace{-2pt} 901t_{\text{REF}}$$

$$t_{\text{PROP}} \hspace{-0.1cm}=\hspace{-0.1cm} 30t_{\text{REF}} + 30t_{\text{REF}} = \hspace{-0.1cm} 60t_{\text{REF}}$$

- Dramatic reduction in t<sub>PROP</sub> is possible (input is driving same in all 3 cases)

- Will later determine what optimal number of stages and sizing is

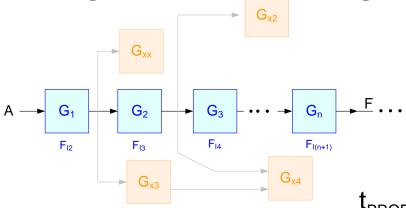

F<sub>lk</sub> denotes the total loading on stage k which is the sum of the F<sub>l</sub> of all loading on stage k

**Summary: Propagation delay from A to F:**

$$\mathbf{t}_{PROP} = \mathbf{t}_{REF} \sum_{k=1}^{n} \frac{\mathbf{F}_{l(k+1)}}{\mathbf{OD}_{k}}$$

Will consider an example with the five cases

- Equal rise/fall (no overdrive)

- Equal rise/fall with overdrive

- Minimum Sized

- Asymmetric Overdrive

- Combination of equal rise/fall, minimum size and overdrive

Will develop the analysis methods as needed

- Equal rise/fall (no overdrive)

- Equal rise/fall with overdrive

- Minimum Sized

- Asymmetric Overdrive

- Combination of equal rise/fall, minimum size and overdrive

$$t_{PROP} = t_{REF} \sum_{k=1}^{n} FI_{(k+1)}$$

$$\mathbf{t}_{PROP} = \mathbf{t}_{REF} \sum_{k=1}^{n} \frac{\mathbf{F}_{I(k+1)}}{\mathbf{OD}_{k}}$$

$$t_{PROP} = ?$$

$$t_{PROP} = ?$$

$$t_{PROP} = ?$$

### **Driving Notation**

Equal rise/fall (no overdrive)

Equal rise/fall with overdrive

Minimum Sized

Asymmetric Overdrive

Notation will be used only if it is not clear from the context what sizing is being used

#### Recall:

Define the Asymmetric Overdrive Factors of the stage to be the factors by which PU and PD resistors are scaled relative to those of the reference inverter.

$$R_{PDEFF} = \frac{R_{PDREF}}{OD_{HL}}$$

$$R_{PUEFF} = \frac{R_{PUREF}}{OD_{LH}}$$

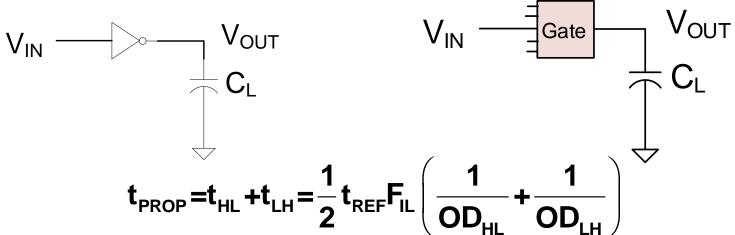

#### **Asymmetric Overdrive**

Recall:

If inverter is not equal rise/fall

$$t_{HL} = \frac{R_{PDREF}}{OD_{HL}}C_{L} = \frac{1}{2}t_{REF}\frac{F_{IL}}{OD_{HL}}$$

$$t_{LH} = \frac{R_{PUREF}}{OD_{LH}}C_{L} = \frac{1}{2}t_{REF}\frac{F_{IL}}{OD_{LH}}$$

$$t_{PROP} = t_{HL} + t_{LH} = \frac{1}{2}t_{REF}F_{IL}\left(\frac{1}{OD_{HL}} + \frac{1}{OD_{LH}}\right)$$

$t_{PROP} = t_{LH} + t_{HL} = t_{REF} \frac{F_{IL}}{OD}$

#### **Asymmetric Overdrive**

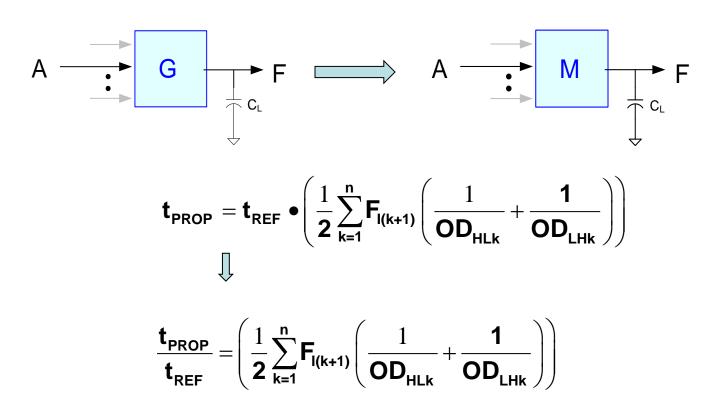

#### When propagating through n stages:

F<sub>lk</sub> denotes the total loading on stage k which the sum of the F<sub>l</sub> of all loading on stage k

$$\mathbf{t}_{\mathsf{PROP}} = \mathbf{t}_{\mathsf{REF}} \bullet \left( \frac{1}{2} \sum_{\mathsf{k=1}}^{\mathsf{n}} \mathbf{F}_{\mathsf{l}(\mathsf{k+1})} \left( \frac{1}{\mathsf{OD}_{\mathsf{HLk}}} + \frac{1}{\mathsf{OD}_{\mathsf{LHk}}} \right) \right)$$

- Equal rise/fall with overdrive

- Minimum Sized

- Asymmetric Overdrive

- Combination of equal rise/fall, minimum size and overdrive

$$t_{PROP} = ?$$

$$t_{PROP} = ?$$

$$t_{PROP} = ?$$

$$t_{PROP} = ?$$

- Equal rise/fall (no overdrive)

- Equal rise/fall with overdrive

- Minimum Sized

- Asymmetric Overdrive

- Combination of equal rise/fall, minimum size and overdrive

$$t_{PROP} = t_{REF} \sum_{k=1}^{n} FI_{(k+1)}$$

$$\mathbf{t}_{PROP} = \mathbf{t}_{REF} \sum_{k=1}^{n} \frac{\mathbf{F}_{I(k+1)}}{\mathbf{OD}_{k}}$$

$$t_{PROP} = ?$$

$$\boldsymbol{t_{\text{PROP}}} = \boldsymbol{t_{\text{REF}}} \bullet \left( \frac{1}{2} \sum_{k=1}^{n} \boldsymbol{F_{\text{I(k+1)}}} \left( \frac{1}{\text{OD}_{\text{HLk}}} + \frac{1}{\text{OD}_{\text{LHk}}} \right) \right)$$

$$t_{PROP} = ?$$

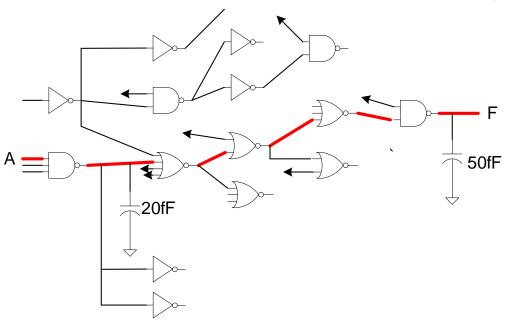

# Propagation Delay in Multiple-Levels of Logic with Stage Loading and Overdrives

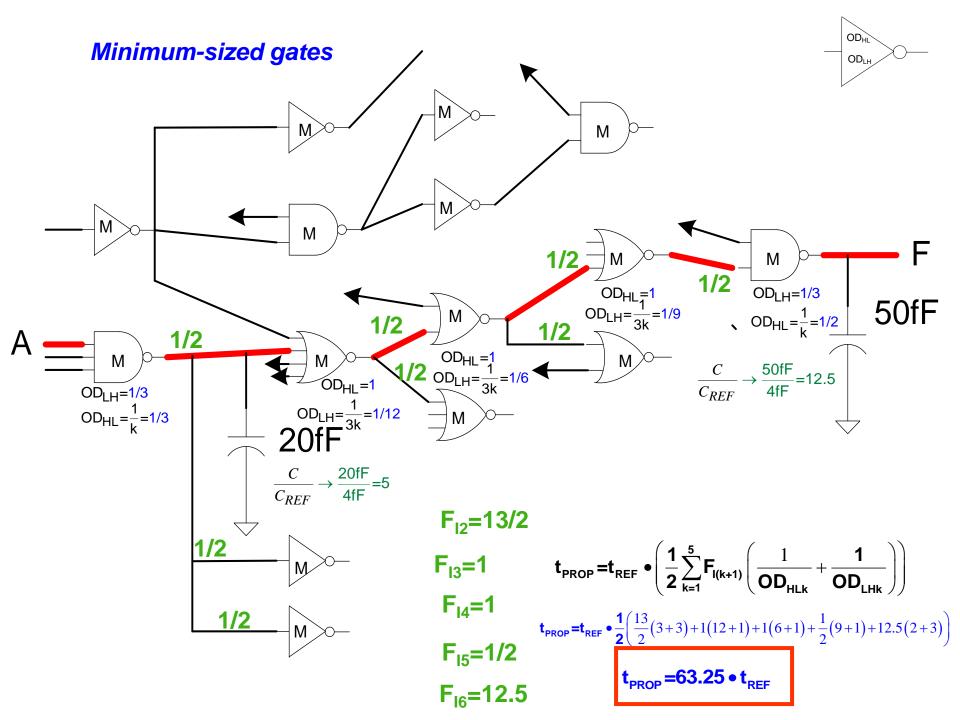

Will now consider A to F propagation for this circuit as an <u>example</u> with different overdrives

- Minimum Sized

- Asymmetric Overdrive

- Combination of equal rise/fall, minimum size and overdrive

$$t_{PROP} = t_{REF} \sum_{k=1}^{n} FI_{(k+1)}$$

$$t_{PROP} = t_{REF} \sum_{k=1}^{n} \frac{F_{I(k+1)}}{OD_{I}}$$

$$t_{PROP} = ?$$

$$\mathbf{t}_{\mathsf{PROP}} = \mathbf{t}_{\mathsf{REF}} \bullet \left( \frac{1}{2} \sum_{k=1}^{n} \mathbf{F}_{\mathsf{I(k+1)}} \left( \frac{1}{\mathsf{OD}_{\mathsf{HLk}}} + \frac{1}{\mathsf{OD}_{\mathsf{LHk}}} \right) \right)$$

$$t_{PROP} = ?$$

Equal rise-fall gates, no overdrive

### Equal rise-fall gates, no overdrive

|                                     | Equal Rise/Fall                      |  |

|-------------------------------------|--------------------------------------|--|

| $C_{\text{IN}}/C_{\text{REF}}$      |                                      |  |

| Inverter                            | 1                                    |  |

| NOR                                 | 3k+1<br>4                            |  |

| NAND                                | 3+k<br>4                             |  |

| Overdrive                           |                                      |  |

| Inverter<br>HL                      | 1                                    |  |

| LH                                  | 1                                    |  |

| NOR<br>HL                           | 1                                    |  |

| LH                                  | 1                                    |  |

| NAND<br>HL                          | 1                                    |  |

| LH                                  | 1                                    |  |

| t <sub>PROP</sub> /t <sub>REF</sub> | $\sum_{k=1}^{n} \mathbf{F}_{l(k+1)}$ |  |

#### Equal rise-fall gates, no overdrive

In 0.5u proc  $t_{REF}$ =20ps,  $C_{REF}$ =4fF, $R_{PDREF}$ =2.5K

(Note: This  $C_{OX}$  is somewhat larger than that in the 0.5u ON process)

#### Equal rise-fall gates, no overdrive

In 0.5u proc  $t_{REF}$ =20ps,  $C_{REF}$ =4fF, $R_{PDREF}$ =2.5K

(Note: This  $C_{OX}$  is somewhat larger than that in the 0.5u ON process)

$$t_{PROP} = 32.5t_{REF}$$

How does this propagation delay compare to that required for a propagation of a signal through 5-levels of logic with only reference inverters (load is a ref inverter instead of 50fF as well)?

$$A \longrightarrow t_{PROP} = 5t_{REF}$$

Loading can have a dramatic effect on propagation delay

# Break here for comments by Jonathan Crandall of Skyworks in Cedar Rapids

Equal rise/fall (no overdrive)

- Minimum Sized

- Asymmetric Overdrive

- Combination of equal rise/fall, minimum size and overdrive

$$t_{PROP} = t_{REF} \sum_{k=1}^{n} FI_{(k+1)}$$

$$t_{PROP} = t_{REF} \sum_{k=1}^{n} \frac{F_{I(k+1)}}{OD_{I}}$$

$$t_{PROP} = ?$$

$$\boldsymbol{t}_{\text{PROP}} = \boldsymbol{t}_{\text{REF}} \bullet \left( \frac{1}{2} \sum_{k=1}^{n} \boldsymbol{F}_{\text{I(k+1)}} \left( \frac{1}{\text{OD}_{\text{HLk}}} + \frac{1}{\text{OD}_{\text{LHk}}} \right) \right)$$

$$t_{PROP} = ?$$

Equal rise-fall gates, with overdrive

In 0.5u proc t<sub>REF</sub>=20ps, C<sub>REF</sub>=4fF,R<sub>PDREF</sub>=2.5K

(Note: This  $C_{OX}$  is somewhat larger than that in the 0.5u ON process)

$$\frac{\mathbf{t}_{PROP}}{\mathbf{t}_{REF}} = \sum_{k=1}^{n} \frac{\mathbf{F}_{\mathbf{l}_{k+1}}}{\mathbf{OD}_{k}}$$

#### Equal rise-fall gates, with overdrive

|                                     | Equal Rise/Fall                               | Equal Rise/Fall<br>(with OD)                                 |  |

|-------------------------------------|-----------------------------------------------|--------------------------------------------------------------|--|

| $C_{\text{IN}}\!/C_{\text{REF}}$    |                                               |                                                              |  |

| Inverter                            | 1                                             | OD                                                           |  |

| NOR                                 | 3k+1<br>4                                     | 3k+1<br>4 • OD                                               |  |

| NAND                                | 3+k<br>4                                      | $\frac{3+k}{4} \bullet OD$                                   |  |

| Overdrive                           |                                               |                                                              |  |

| Inverter<br>HL                      | 1                                             | OD                                                           |  |

| LH                                  | 1                                             | OD                                                           |  |

| NOR<br>HL                           | 1                                             | OD                                                           |  |

| LH                                  | 1                                             | OD                                                           |  |

| NAND<br>HL                          | 1                                             | OD                                                           |  |

| LH                                  | 1                                             | OD                                                           |  |

| t <sub>PROP</sub> /t <sub>REF</sub> | $\sum_{k=1}^{n} \mathbf{F}_{\mathbf{l}(k+1)}$ | $\sum_{k=1}^{n} \frac{\textbf{F}_{I(k+1)}}{\textbf{OD}_{k}}$ |  |

#### Equal rise-fall gates, with overdrive

than that in the 0.5u ON process)

#### Minimum-sized gates

In 0.5u proc t<sub>REF</sub>=20ps, C<sub>REF</sub>=4fF,R<sub>PDREF</sub>=2.5K

$$\mathbf{t}_{\mathsf{PROP}} = \mathbf{t}_{\mathsf{REF}} \bullet ?$$

- Equal rise/fall (no overdrive)

- Equal rise/fall with overdrive

- Minimum Sized

- Asymmetric Overdrive

- Combination of equal rise/fall, minimum size and overdrive

$$t_{PROP} = t_{REF} \sum_{k=1}^{n} Fl_{(k+1)}$$

$$t_{PROP} = t_{REF} \sum_{k=1}^{n} \frac{F_{I(k+1)}}{OD_k}$$

$$t_{PROP} = ?$$

$$\boldsymbol{t_{\text{PROP}}} = \boldsymbol{t_{\text{REF}}} \bullet \left( \frac{1}{2} \sum_{k=1}^{n} \boldsymbol{F_{\text{I(k+1)}}} \left( \frac{1}{\text{OD}_{\text{HLk}}} + \frac{1}{\text{OD}_{\text{LHk}}} \right) \right)$$

$$t_{PROP} = ?$$

Minimum-sized gates

$\mathbf{t}_{\mathsf{PROP}} = \mathbf{t}_{\mathsf{REF}} \bullet ?$

Observe that a minimum-sized gate is simply a gate with asymmetric overdrive

#### Recall:

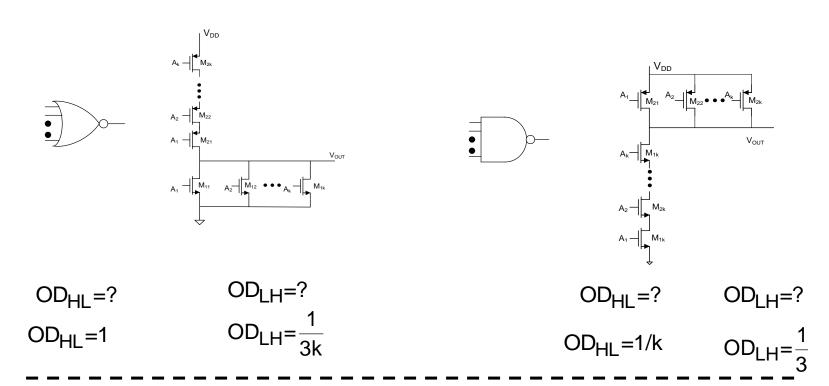

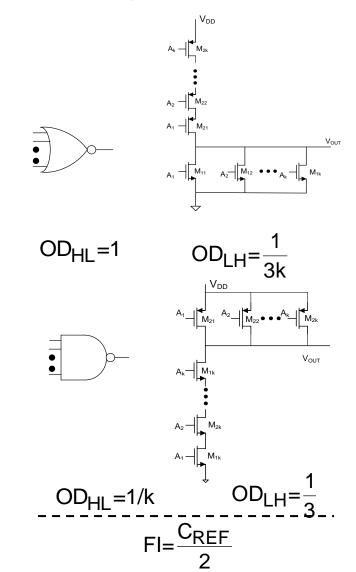

### Propagation Delay with Minimum-Sized Gates

- Still need OD<sub>HL</sub> and OD<sub>LH</sub> for minimum-sized gates

- Still need FI for minimum-sized gates

### Propagation Delay with minimum-sized gates

$FI=2C_{OX}W_{MIN}L_{MIN}$

$C_{REF} = 4C_{OX}W_{MIN}L_{MIN}$

$$FI = \frac{C_{REF}}{2}$$

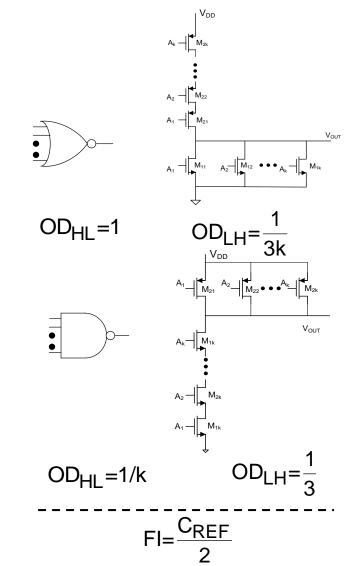

#### Minimum-sized gates

|                                     | Equal Rise/Fall           | Equal Rise/Fall<br>(with OD)                                 | Minimum Sized |

|-------------------------------------|---------------------------|--------------------------------------------------------------|---------------|

| $C_{\text{IN}}/C_{\text{REF}}$      |                           |                                                              |               |

| Inverter                            | 1                         | OD                                                           |               |

| NOR                                 | 3k+1<br>4                 | 3k+1 • OD                                                    |               |

| NAND                                | 3+k<br>4                  | $\frac{3+k}{4} \bullet OD$                                   |               |

| Overdrive                           |                           |                                                              |               |

| Inverter<br>HL                      | 1                         | OD                                                           |               |

| LH                                  | 1                         | OD                                                           |               |

| NOR<br>HL                           | 1                         | OD                                                           |               |

| LH                                  | 1                         | OD                                                           |               |

| NAND<br>HL                          | 1                         | OD                                                           |               |

| LH                                  | 1                         | OD                                                           |               |

| t <sub>PROP</sub> /t <sub>REF</sub> | $\sum_{k=1}^n F_{l(k+1)}$ | $\sum_{k=1}^{n} \frac{\mathbf{F}_{l(k+1)}}{\mathbf{OD}_{k}}$ |               |

#### Minimum-sized gates

|                                     | Equal Rise/Fall           | Equal Rise/Fall<br>(with OD)             | Minimum Sized                                                                                  |

|-------------------------------------|---------------------------|------------------------------------------|------------------------------------------------------------------------------------------------|

| $C_{\text{IN}}/C_{\text{REF}}$      |                           |                                          |                                                                                                |

| Inverter                            | 1                         | OD                                       | 1/2                                                                                            |

| NOR                                 | 3k+1<br>4                 | 3k+1 ◆ OD                                | 1/2                                                                                            |

| NAND                                | 3+k<br>4                  | 3+k<br>4 • OD                            | 1/2                                                                                            |

| Overdrive                           |                           |                                          |                                                                                                |

| Inverter<br>HL                      | 1                         | OD                                       | 1                                                                                              |

| LH                                  | 1                         | OD                                       | 1/3                                                                                            |

| NOR<br>HL                           | 1                         | OD                                       | 1                                                                                              |

| LH                                  | 1                         | OD                                       | 1/(3k)                                                                                         |

| NAND<br>HL                          | 1                         | OD                                       | 1/k                                                                                            |

| LH                                  | 1                         | OD                                       | 1/3                                                                                            |

| t <sub>PROP</sub> /t <sub>REF</sub> | $\sum_{k=1}^n F_{l(k+1)}$ | $\sum_{k=1}^{n} \frac{F_{l(k+1)}}{OD_k}$ | $\frac{1}{2} \sum_{k=1}^{n} F_{I(k+1)} \left( \frac{1}{OD_{HLk}} + \frac{1}{OD_{LHk}} \right)$ |

#### Minimum-sized gates

|                                     | Equal Rise/Fall                          | Equal Rise/Fall<br>(with OD)           | Minimum Sized                                                                                  |

|-------------------------------------|------------------------------------------|----------------------------------------|------------------------------------------------------------------------------------------------|

| $C_{\text{IN}}/C_{\text{REF}}$      |                                          |                                        |                                                                                                |

| Inverter                            | 1                                        | OD                                     | 1/2                                                                                            |

| NOR                                 | 3k+1<br>4                                | 3k+1 • OD                              | 1/2                                                                                            |

| NAND                                | 3+k<br>4                                 | 3+k / 4 • OD                           | 1/2                                                                                            |

| Overdrive                           |                                          |                                        |                                                                                                |

| Inverter<br>HL                      | 1                                        | OD                                     | 1                                                                                              |

| LH                                  | 1                                        | OD                                     | 1/3                                                                                            |

| NOR<br>HL                           | 1                                        | OD                                     | 1                                                                                              |

| LH                                  | 1                                        | OD                                     | 1/(3k)                                                                                         |

| NAND<br>HL                          | 1                                        | OD                                     | 1/k                                                                                            |

| LH                                  | 1                                        | OD                                     | 1/3                                                                                            |

| t <sub>PROP</sub> /t <sub>REF</sub> | $\sum_{k=1}^{n} \boldsymbol{F}_{l(k+1)}$ | $\sum_{k=1}^n \frac{F_{l(k+1)}}{OD_k}$ | $\frac{1}{2} \sum_{k=1}^{n} F_{I(k+1)} \left( \frac{1}{OD_{HLk}} + \frac{1}{OD_{LHk}} \right)$ |

- Equal rise/fall (no overdrive)

- Equal rise/fall with overdrive

- Minimum Sized

- Asymmetric Overdrive

- Combination of equal rise/fall, minimum size and overdrive

$$t_{PROP} = t_{REF} \sum_{k=1}^{n} FI_{(k+1)}$$

$$\mathbf{t}_{PROP} = \mathbf{t}_{REF} \sum_{k=1}^{n} \frac{\mathbf{F}_{I(k+1)}}{\mathbf{OD}_{k}}$$

$$\mathbf{t}_{\mathsf{PROP}} = \mathbf{t}_{\mathsf{REF}} \bullet \left( \frac{1}{2} \sum_{k=1}^{n} \mathbf{F}_{\mathsf{I(k+1)}} \left( \frac{1}{\mathsf{OD}_{\mathsf{HLk}}} + \frac{1}{\mathsf{OD}_{\mathsf{LHk}}} \right) \right)$$

$$\mathbf{t}_{\mathsf{PROP}} = \mathbf{t}_{\mathsf{REF}} \bullet \left( \frac{1}{2} \sum_{k=1}^{n} \mathbf{F}_{\mathsf{I(k+1)}} \left( \frac{1}{\mathsf{OD}_{\mathsf{HLk}}} + \frac{1}{\mathsf{OD}_{\mathsf{LHk}}} \right) \right)$$

$$t_{PROP} = ?$$

### Stay Safe and Stay Healthy!

### **End of Lecture 41**